Europejska technologia traci na znaczeniu. ASML może mieć problem

W najbliższych latach czeka nas popularyzacja GAA FET i CFET przy produkcji półprzewodników. Tym samym kluczowe staną się inne etapy procesu.

Według jednego z dyrektorów Intela, przyszłe generacje tranzystorów mogą zmienić sposób produkcji najbardziej zaawansowanych układów scalonych, czyniąc zaawansowane maszyny litograficzne - takie jak urządzenia EUV produkowane przez ASML - mniej kluczowymi dla całego procesu.

Większy nacisk podczas produkcji będzie położny na tzw. trawienie

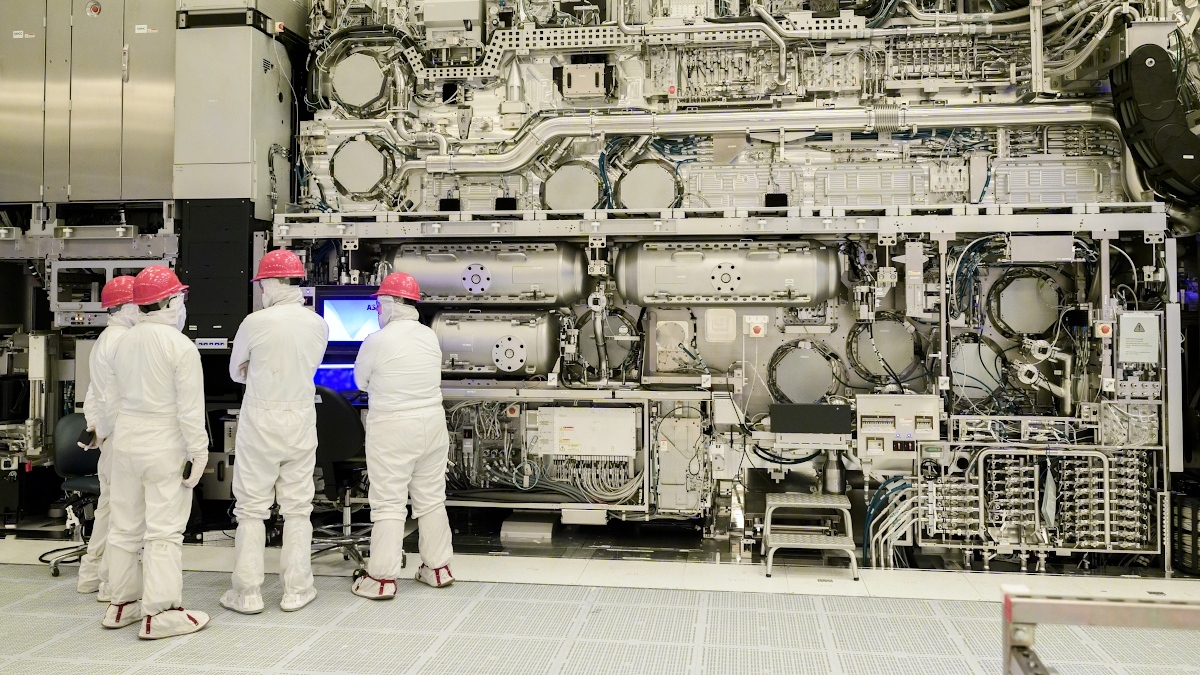

Holenderskie maszyny są obecnie fundamentem nowoczesnej produkcji półprzewodników. To dzięki nim firmy jak TSMC mogą tworzyć niezwykle małe obwody na krzemowych płytkach. Jednak nadchodzące projekty tranzystorów - takie jak gate-all-around FET (GAA FET) i complementary FET (CFET) - będą w większym stopniu opierać się na etapach produkcji po litografii, a nie na samej litografii.

Anonimowy dyrektor Intela wskazuje, że większe znaczenie zyska technologia trawienia (tzw. etching). Chociaż najbardziej zaawansowane skanery EUV i high-NA EUV są najczęściej omawianymi elementami procesu ze względu na ograniczenia eksportowe i ich wysoką cenę, produkcja chipów obejmuje także inne kluczowe etapy.

Litografia to tylko pierwszy krok - to ona przenosi wzory układów na płytkę. Następnie przez procesy takie depozycja i trawienie wzory te są fizycznie utrwalane. Podczas gdy depozycja polega na nakładaniu materiału na płytkę, trawienie pozwala na jego selektywne usuwanie, tworząc odpowiednie struktury tranzystorów i obwodów.

W dotychczasowych projektach (np. FinFET) tranzystory są łączone z materiałem izolacyjnym u podstawy, a przepływem prądu steruje bramka z jednej strony. W nowych układach GAA FET bramka otacza tranzystor z każdej strony, a grupy tranzystorów są rozmieszczone równolegle. Z kolei CFET idzie o krok dalej - tranzystory są ułożone warstwowo, co pozwala zaoszczędzić przestrzeń na płytce.

W takich układach kluczowe staje się precyzyjne usuwanie materiału - nie tylko w pionie, ale i w poziomie. "Otulenie" tranzystora przez bramkę wymaga wyjątkowo dokładnego trawienia bocznego. Zamiast więc zwiększać czas ekspozycji w maszynie litograficznej w celu zmniejszania rozmiarów elementów, producenci będą skupiać się na zaawansowanym trawieniu, które umożliwia uzyskanie większej gęstości tranzystorów bez dalszego zmniejszania cech litograficznych.

To podejście może zredukować znaczenie maszyn high-NA EUV, które - według dyrektora Intela - "najprawdopodobniej nie będą już tak kluczowe, jak skanery EUV były dla produkcji chipów w technologiach 7 nm i mniejszych". W rezultacie zmniejsza się zależność od minimalnych cech litograficznych, ponieważ wysoką gęstość można osiągać nie tylko na jednej płaszczyźnie, ale także w pionie. To oznacza zmianę kierunku rozwoju całej branży.